五部门关于开展2024年新能源汽车下乡活动的通知

栅极长度缩放超出硅的 FET 对短沟道效应具有鲁棒性

栅极长度缩放超出硅的 FET 对短沟道效应具有鲁棒性 自从在现代电子产品中引入场效应晶体管 (FET) 以来,理论和应用电路技术已经取得了多项改进。FET 是低频和中频的低噪声

自从在现代电子产品中引入场效应晶体管 (FET) 以来,理论和应用电路技术已经取得了多项改进。FET 是低频和中频的低噪声放大器以及高输入阻抗放大器、电荷敏感放大器和模拟乘法器的理想选择。此外,它们还可以用作可变反馈元件。由于 FET 在控制电路和 JFET 电压表设计中的互调失真,因此在混合电路中实现。

当今行业中发现的大多数 FET 都是由硅制成的,因为它具有出色且可重现的电子特性。根据摩尔定律,硅受到薄通道厚度下迁移率下降的困扰,这为高度缩放的设备保持强静电。过渡金属二硫化物 (TMD) 等二维沟道材料可用于 FET 以解决此问题。由于2D 材料具有二维表面,因此它们具有更好的迁移率水平,包括在 0.7 A 下实现激进的沟道长度缩放。

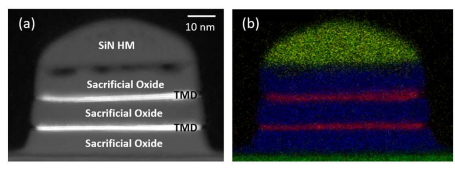

二维纳米片具有独特的特性,使其在分离应用中具有吸引力。它们具有高表面积与体积比、可调孔径和高机械稳定性。这些特性允许有效的分子传输和分离,使它们成为用于各个领域的有前途的材料。图 1 显示了堆叠的 2D 纳米片结构,其中 TMD 层与牺牲氧化物层交替出现。在类似的条件下,2D CMOS 也可以与这种分层堆栈集成,支持减少栅极长度和增加每个堆栈高度的几个通道。

缩放 L S-D设备的制造为了通过启用短沟道 2D 晶体管来缩放 L S-D和栅极氧化物,构建了一种器件制造以获得更好的静电特性。初,使用湿转移法将 MBE 生长的 MoS 2单层转移到TiN 上的 5 nm HfO 2底栅基板上。在设备运行期间具有重要作用的主要尺寸可以通过使用 FWHM 的电子束光斑尺寸来确定,在高分辨率模式下范围小于 10 nm。在生产 L S-D尺寸小于 25 nm 且样品之间的差异较小时,使用了 PMMA 抗蚀剂工艺。

尽管即使在较小的尺寸下,薄光刻胶方法也会导致 L S-D的变化较小,但它可能是清洁剥离过程中的方法。观察了具有 HfO 2底栅氧化物和薄的 Al 2 O 3 /HfO 2双层顶栅氧化物的双栅器件的 TEM 。

二维通道的静电在研究 2D 单层通道的 SCE 时,探测了单门控器件传输特性,范围从超过 50 nm 的长 L S-D到25 nm 的缩放 L S-D 。这些晶体管具有单栅极配置,其中随着 L S-D上升到L S-D = 35 nm 以下,SS 显示出退化迹象,同时中值漏极感应势垒降低 (DIBL) 增加至 132 mV/V。

当谈到理想的 2D 晶体管的功能时,人们认为它们不会在这种缩放下体验 SCE。当安装额外的顶栅时,在长 L S-D处观察到静电增强,其中更陡峭的 SS位于75 mV/dec 附近,低 DIBL 为 12 mV/V 。

还使用 Sentaurus 设备执行了 TCAD 模拟,其中可以在数据中看到实时趋势以用于实验目的。介电常数k = 1 被建模为底部 HfO 2中的空隙以简化结构。

在模拟中,很明显在触点边缘存在MoS 2分层,这会产生劣化的 SS。在实验过程中,在 Al 2 O 3的界面处添加固定正电荷以在双栅极器件中复制更陡峭的 SS。DIBL 与每个 L S-D的 SS 扩散之间也存在正相关关系,这表明静电控制因设备而异。此外,对于遭受随机转移残留物和未钝化 TMD 通道的双门控长 L S-D器件,观察到变化减少。

栅极氧化物优化的三甲基铝 (TMA) 和 H 2 O 暴露用于120°C 的低温 Al 2 O 3沉积,这特别适用于顶部氧化物栅极。基于进行的AFM分析,所产生的HfO 2 /Al 2 O 3双层形成有约0.5nm的RMS粗糙度。由于栅极几乎短路,大约 25% 的双栅极器件会“失效”,同时,20% 的器件会遭受高栅极漏电。55% 的器件表现出高均匀性和极低的栅极泄漏。此外,由于引脚之间的平均距离,针孔可能会包含在部分器件的沟道区域内,这可能会导致栅极泄漏故障。

很明显,无针孔“薄双层”ALD 氧化膜具有高内在质量,这是基于该组器件的低均匀栅极泄漏。薄双层设计专门用于稳定薄的栅极氧化物,并通过提供薄且高质量的栅极氧化物同时确保对底层材料的充分覆盖和保护来帮助实现这种平衡。单门控和双门控测量的迟滞几乎为零,这表明栅极氧化物/TMD 界面的质量很高。

结论使用双层 ALD 工艺对二维晶体管静电进行了统计研究,该工艺具有与二维表面兼容的薄高 k 表面。根据实验和模拟数据,二维单层通道具有非常薄的主体。尽管 2D 晶体管的栅极氧化物厚度和界面没有优化,但它们对短沟道效应(尤其是 DIBL)表现出非常好的抵抗力。因此,二维 TMD 单层可以被确定为合适的通道材料来替代硅,以保持摩尔定律的缩放比例。

上一篇:推进新型反激式转换器的同步整流器

-

美研究人员发现电池过热问题出在电池材料表面 添加氧化物涂层或可解决2019-05-12

-

美国大学发现电池过热问题出在电池材料表面 添加氧化物涂层或可解决2019-05-12

-

着眼固体氧化物电池 博世入股英国公司2018-08-26

-

铌钨氧化物电极或能实现电动车电池快充2018-08-06

-

韩科院研发一项新技术 提升固体氧化物燃料电池的稳定性2018-01-23

-

日产全球首推固态氧化物燃料电池车,续航600公里2016-08-09

-

日产推出世界首款固态氧化物燃料电池车2016-08-08